# 72W Offline Flyback Converter Using the MAX17595

MAXREFDES1037

#### Introduction

The MAX17595 is a peak-current-mode controller for designing wide input-voltage flyback regulators. The MAX17595 offers optimized input thresholds for universal input AC-DC converters and telecom DC-DC (36V to 72V input range) power supplies. It contains a built-in gate driver for an external n-channel MOSFET. The MAX17595 houses an internal error amplifier with 1% accurate reference, eliminating the need for an external reference. The switching frequency is programmable from 100kHz to 1MHz with an accuracy of 8%, allowing optimization of magnetic and filter components, resulting in compact and cost-effective power conversion. For EMI-sensitive applications, the MAX17595 incorporates a programmable frequency dithering scheme, enabling low-EMI spread-spectrum operation. Users can start the power supply precisely at the desired input voltage, implement input overvoltage protection, and program soft-start time. A programmable slope compensation scheme is provided to ensure stability of the peak current-mode control scheme. Hiccup-mode overcurrent protection and thermal shutdown are provided to minimize dissipation in overcurrent and overtemperature fault conditions.

- Programmable Switching Frequency Allows Optimization of the Magnetic and Filter Components, Resulting in Compact, Cost-Effective, Efficient Isolated/ Nonisolated Power Supplies

- 100kHz to 1MHz Programmable Switching Frequency with Optional Synchronization

- Peak Current Mode Control Provides Excellent Transient Response—Offline (Universal Input AC) and Telecom (36V to 72V) Flyback Controller

- Programmable Frequency Dithering Enables Low EMI Spread-Spectrum Operation

- Integrated Protection Features Enhance System Reliability

- Adjustable Current Limit with External Current Sense Resistor

- Fast Cycle-By-Cycle Peak Current Limiting Hiccup-Mode Short-Circuit Protection

- Overtemperature Protection

- Programmable Soft-Start and Slope Compensation

- Input Overvoltage Protection

## **Hardware Specification**

An offline DCM flyback converter using the MAX17595 is demonstrated for a 24V DC output application. The power supply delivers up to 3A at 24V. Table 1 shows an overview of the design specification.

**Table 1. Design Specification**

| PARAMETER             | SYMBOL           | MIN                        | MAX |

|-----------------------|------------------|----------------------------|-----|

| Input Voltage         | V <sub>IN</sub>  | 103V AC   128V AC          |     |

| Frequency             | f <sub>SW</sub>  | 125kHz                     |     |

| Maximum Efficiency    | η                | 86.7%                      |     |

| Output Voltage        | V <sub>OUT</sub> | 24V                        |     |

| Output Voltage Ripple | $\Delta V_{OUT}$ | 1% of V <sub>OUT</sub> max |     |

| Output Current        | I <sub>OUT</sub> | 0 3A                       |     |

| Output Power          | P <sub>OUT</sub> | 72W                        |     |

## Designed-Built-Tested

This document describes the hardware shown in Figure 1. It provides a detailed systematic technical guide to designing an offline discontinuous conduction mode (DCM) flyback using Maxim's MAX17595 current-mode controller. The power supply has been built and tested, details of which follow later in this document.

Figure 1. MAXREFDES1037 hardware.

Rev 3; 7/18 Maxim Integrated | 1

## **Generic Isolated Power Supply**

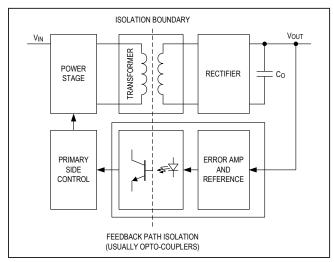

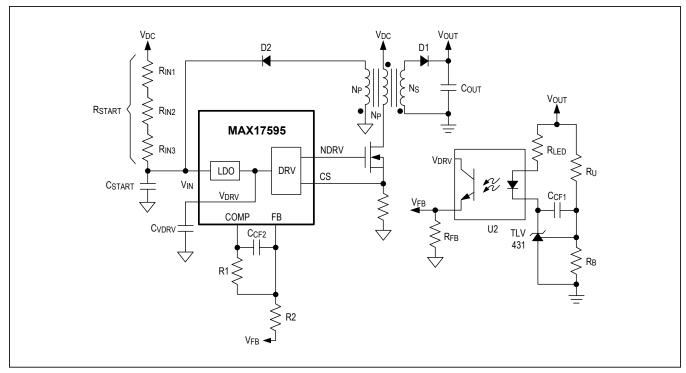

Figure 2 shows a generic isolated power-supply block diagram. It consists of a power stage, an isolation transformer, rectifier, secondary-side error amplifier, and opto-coupler to provide a feedback for the primary side control. Different isolated power supplies are different depending upon how the transformer is being used in them.

Figure 2. Generic isolated power supply.

#### Flyback Principle

A transformer in a flyback configuration acts differently than its usual operation of transformation of energy from primary to secondary. During a transformer's usual operation, both primary and secondary windings conduct together at the same time to make the transfer of energy possible from primary to secondary. In a flyback configuration the primary and secondary windings do not conduct at the same time and the transformer acts more like a coupled inductor. Note that in this document we have used the following notations for the transformer turns ratio:

$$K = \frac{N_P}{N_S}$$

$$k = \frac{N_S}{N_P}$$

This means capital K for primary turns/secondary turns and small k for secondary turns/primary turns.

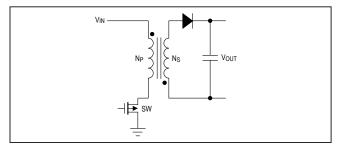

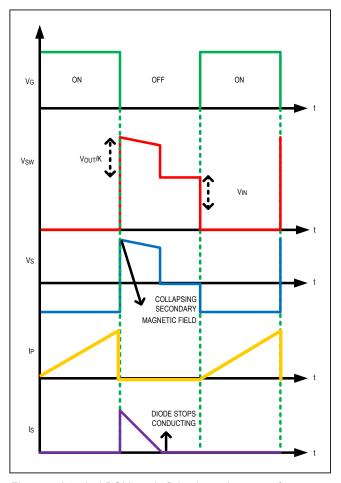

Figure 3 shows a simple flyback topology that consists of a transformer whose primary winding is connected to the drain of a switching MOSFET. The source of the MOSFET is connected to ground. The secondary winding is connected to the output capacitor through a rectifier diode. In this flyback configuration the current flows into the primary winding during the on time of the switching period and flows into the secondary winding during the off time of the switching period.

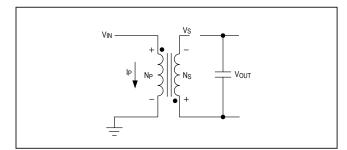

During the on-time when the primary switch is closed, a current,  $I_P$ , flows through the primary winding as shown in Figure 4.  $I_P$  can be written as follows:

$$I_P(t) = \frac{1}{L_P} \int_0^t V_{IN} d\tau = \frac{1}{L_P} V_{IN} t$$

The peak magnitude of the primary current can be written as follows:

$$I_{P-P} = \frac{1}{L_P} \int_{0}^{t_{ON}} V_{IN} d\tau = \frac{1}{L_P} V_{IN} t_{ON}$$

In the secondary winding, a negative voltage is induced due to the current flowing in to the primary. The rectifier diode is reverse-biased and no current is flowing in the secondary winding. The induced voltage in the primary can be written as:

$$V_S(t) = L_S \times \frac{dI_P(t)}{dt}$$

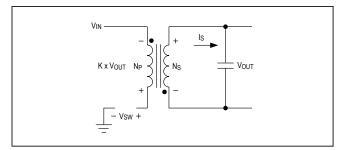

During the off-time when the primary switch opens as shown in Figure 5, the magnetic field in the primary winding collapses and the voltage at the winding reverses, while current keeps flowing in the same direction until the field fades away.

The secondary current  $I_S$  flows and the secondary and rectifier diode is forward-biased. Output voltage  $V_{OUT}$  is now available across the secondary coil if we ignore the forward voltage drop of the rectifier diode. The secondary winding voltage is now flown away to primary side as K x  $V_{OUT}$ . This voltage is present across the switch until the current in the secondary winding decays to zero. Total voltage available across the switch during the off-time can be written as:

$$V_{SW} = V_{IN} + K \times V_{OUT}$$

This voltage also causes the breakdown of the magnetic flux in the primary winding (no current is flowing in the primary winding after this reset). Here we can see that unlike a usual transformer action where current flows in both the winding at the same time, in a flyback transformer the current flows into the primary winding during the on-time and into the secondary winding during the off-time. This is why we use the term "coupled storage inductor" for transformers used in flyback operation. It should be noted though that mechanically these transformers are like any transformer. Use in flyback operations makes transformers act differently as coupled inductors. The required duty cycle for a given input voltage and output voltage can be calculated from:

$$D = \frac{V_{OUT}}{V_{OUT} + V_{IN}}$$

where:

$$V_{OUT} = (V_{OUT} + V_F) \times \frac{N_P}{N_S}$$

www.maximintegrated.com Maxim Integrated | 2

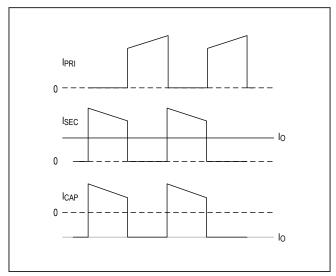

Figure 6 shows a typical CCM mode flyback primary and secondary winding current, and Figure 7 shows a typical DCM mode flyback waveform.

Figure 3. Simple flyback topology.

Figure 4. Flyback topology during on-time,  $t_{\rm ON}$ .

Figure 5. Flyback topology during off-time, t<sub>OFF</sub>.

Figure 6. A typical CCM mode flyback primary and secondary winding current.

Figure 7. A typical DCM mode flyback topology waveform.

# **Design Procedure for Offline Flyback Using MAX17595**

Now that the basic principle of the DCM flyback is understood, a practical design can be illustrated. The design parameters are obtained by using expressions given in Maxim **Application Note 5504**. This document is primarily concerned with the power stage and the feedback loop design, and is intended to complement the information contained in the MAX17595 data sheet.

Flyback converters can be operated in discontinuous conduction mode (DCM) or continuous conduction mode (CCM). The component choices, stress level in power devices, and controller design vary depending on the operating mode of the converter. The design discussed in this document is a DCM design and expressions for calculating component values and ratings are presented to achieve the design goals.

#### **Step 1: Switching Frequency**

For offline flyback operation, the selection of switching frequency is of prime importance. Thermal limits and junction temperature of the device limits the selected switching frequency to be less than 150kHz. For this design we have selected a switching frequency of 125kHz. The MAX17595 switching frequency is programmable between 100kHz and 1000kHz with a resistor  $R_{\rm RT}$  connected between RT and SGND. The  $R_{\rm RT}$  is calculated as follows:

$$R_{RT} = \frac{10^{10}}{f_{SW}} \Omega$$

$$R_{RT} = \frac{10^{10}}{125k} = 80k\Omega$$

A standard  $80.6k\Omega$  resistor is selected for  $R_{RT}$ .

# Step 2: Transformer Magnetizing Inductance and Turns Ratio

In a DCM flyback converter, the energy stored in the primary inductance of the flyback transformer is delivered entirely to the output. The maximum primary-inductance value for which the converter remains in DCM at all operating conditions can be calculated as:

$$L_{PRI} \le \frac{0.4 \times \left(V_{INMIN} \times D_{MAX}\right)^{2}}{\left(V_{OUT} + V_{D}\right) \times I_{OUT} \times f_{sw}}$$

where:

$D_{MAX} = 0.43V$

$V_{\rm D}$  = 0.58V is the forward voltage drop of the rectifier diode of the secondary winding.

In this offline application, the DC bus voltage varies from 145.6V DC to 181V DC. But the actual minimum input operating voltage depends on the 100Hz ripple present on the DC bus capacitor. In this application, the ripple is assumed to be 30V and hence the minimum DC input to the converter.

$$V_{INMIN} = 176 \times 1.414 - 30 = 218.9V$$

Substituting the above values in the expression of  $L_{\text{MAG}}$  as follows:

$$L_{PRI} \le \frac{0.4 \times (218.9 \times 0.43)^2}{5.1 \times 0.7 \times 125 k} = 7941 \mu H$$

To account for 10% tolerance in primary inductance for our design,  $L_{MAG}$  is chosen as  $97\mu H$ ,  $L_{PRI}$  =  $97\mu H$ .

The leakage inductance of the transformer should be targeted as low as possible. For this design, we achieved a 1.5% leakage inductance of  $1.46\mu$ H,  $L_{LKG} = 1.46\mu$ H.

A customized transformer 750317114 from Würth Electronik is used in this design. This transformer also fulfills the specification of turns ratio, bias winding, and primary/secondary currents requirement of the design that is calculated step by step in this document. The transformer has dielectric isolation specification of 3500V AC.

# **Step 3: Maximum Duty Cycle Calculation** with Selected Lpri

Use the following expressions to calculate the maximum duty cycle of the converter for the selected frequency and magnetizing inductance:

$$D_{NEW} = \frac{\sqrt{2.5 \times L_{PRI} \times V_{OUT} \times I_{OUT} \times f_{SW}}}{V_{INMIN}}$$

$$D_{NEW} = \frac{\sqrt{2.5 \times 3m \times 5 \times 0.7 \times 125k}}{218.9} = 0.261$$

Calculate the required transformer turns ratio (k) using the expressions as follows:

$$\begin{aligned} k &= \frac{N_S}{N_p} = \frac{(V_{OUT} + V_D) \times (1 - D_{NEW})}{D_{NEW} \times V_{INMIN}} \\ k &= \frac{N_S}{N_p} = \frac{(5 + 0.1) \times (1 - 0.261)}{0.261 \times 218.9} = 0.065 \end{aligned}$$

For the present design, k is chosen as 1:312.

#### Step 4: Calculation of Peak/RMS Current

Primary and secondary RMS and primary peak currents calculations are needed to design the transformer in switched-mode power supplies. Also, primary peak current is used in setting the current limit. Use the following expressions to calculate the primary and secondary peak and RMS currents.

$$\begin{split} I_{PRIPEAK} &= \frac{V_{INMIN} \times D_{NEW}}{L_{PRI} \times f_{SW}} = \frac{218.9 \times 0.261}{3m \times 125 kHz} = 0.1527A \\ I_{PRIRMS} &= I_{PRIPEAK} \times \sqrt{\frac{D_{NEW}}{3}} = 0.1527 \times \sqrt{\frac{0.261}{3}} = 0.045A \\ I_{SECPEAK} &= \frac{I_{PRIPEAK}}{k} = \frac{0.1527}{0.065} = 2.323A \\ I_{SECRMS} &= \sqrt{\frac{2 \times I_{OUT} \times I_{PRIPEAK}}{3 \times k}} = 1.04A \end{split}$$

#### **Step 5: Current Limit Resistor Calculation**

For current limit setting, the peak current can be calculated as follows:

$$I_{LIM} = 1.2 \text{ x } I_{PRIPEAK} = 1.2 \text{ x } 3.84 = 4.6 \text{A}$$

The device includes a robust overcurrent protection scheme that protects the device under overload and short-circuit conditions. A current-sense resistor, connected between the source of the MOSFET and PGND, sets the peak current limit. The current-limit comparator has a voltage trip level ( $V_{\text{CS-PEAK}}$ ) of 300mV. Use the following equation to calculate the value of  $R_{\text{CS}}$ :

$$R_{CS} = \frac{305m}{I_{MOSEFT}} = \frac{305m}{0.1833} = 1663m\Omega$$

where  $I_{MOSFET}$  is the peak current flowing through the MOSFET. A typical  $68m\Omega$  current-sense resistor is selected,  $R_{CS}$  =  $68m\Omega.$

#### **Step 6: MOSFET Selection**

MOSFET selection criteria includes maximum drain voltage, peak/RMS current in the primary, and the maximum allowable power dissipation of the package without exceeding the junction temperature limits. The voltage seen by the MOSFET drain is the sum of the input voltage, the reflected secondary voltage on the transformer primary, and the leakage inductance spike. The MOSFET's absolute maximum  $V_{DS}$  rating must be higher than the worst-case drain voltage as follows:

$$V_{DSMAX} = V_{INMAX} + \left(\frac{2.5 \times (V_{OUT} + Vd)}{k}\right)$$

$$V_{DSMAX} = 401.6 + \left(\frac{2.5 \times (5 + 0.1)}{0.065}\right) = 595.6V$$

For this application, the 400V 10A n-channel MOSFET IRF740AS from Vishay is selected as the primary MOSFET.

#### **Step 7: Snubber Selection**

RCD snubbers reduce the maximum voltage stress on the MOSFET by clamping the voltage level. However, they also dissipate power and reduce efficiency. They might not always be required, however it is always a good idea to leave place holders in the board for RCD and RC snubbers. Ideally, the external MOSFET experiences a drain-source voltage stress equal to the sum of the input voltage and reflected voltage across the primary winding during the off period of the MOSFET. In practice, parasitic inductors and capacitors in the circuit, such as leakage inductance of the flyback transformer, cause voltage overshoot and ringing in addition to the ideally expected voltage stress. Snubber circuits are used to limit the voltage overshoots to safe levels within the voltage rating of the external MOSFET. The snubber capacitor can be calculated using the following expression:

$$C_{SNUB} = \frac{2 \times L_{LK} \times I_{PRIPEAK}^{2} \times k^{2}}{V_{OUT}^{2}}$$

$$C_{SNUB} = \frac{2 \times 45 \mu \times 0.152^{2} \times 0.065^{2}}{5^{2}} = 362.9 pF$$

Considering the derating of the capacitor, we selected a capacitor of value 8200pF,  $C_{\text{SNUB}}$  = 8200pF.

Figure 8. Bias winding configuration.

The power that must be dissipated in the snubber resistor is calculated using the following expressions:

$$P_{SNUB} = 0.833 \text{ x } L_{LKG} \text{ x } I_{PRIPEAK}^2 \text{ x } f_{SW}$$

$P_{SNUB} = 0.833 \text{ x } 1.46 \mu \text{ x } 3.84^2 \text{ x } 125 k = 2.25 W$

The snubber resistor is calculated based on the below expression:

$$R_{SNUB} = \frac{6.25 \times V_{OUT}^2}{P_{SNUB} \times k^2} = \frac{6.25 \times 5^2}{0.109 \times 0.065^2} = 330.7 k\Omega$$

A standard resistor of 16k $\Omega$  3W 1.5W is selected, R<sub>SNUB</sub> = 16k $\Omega$ .

The voltage rating of the snubber diode is:

$$VD_{SNUB} = V_{INMAX} + (2.5 \times \frac{V_{OUT}}{k})$$

$$VD_{SNUB} = 401.2 + (2.5 \times \frac{5}{0.065}) = 591.79V$$

An 400V, 2A diode ES2G-E3 from Vishay is selected as the snubber diode for this design.

#### **Step 8: Selection of Secondary Rectifier Diode**

The maximum operating reverse-voltage rating of the secondary rectifier diode must be higher than the sum of the output voltage and the reflected input voltage. We use

the following expression to calculate the secondary diode voltage rating:

$$V_{SEC,DIODE} = 1.25 \text{ x (k x } V_{INMAX} + V_{OUT})$$

$V_{SEC,DIODE} = 1.25 \text{ x (0.312 x 181 + 24)} = 100.6 \text{V}$

The current rating of the secondary diode should be selected so that the power loss in the diode (given as the product of forward-voltage drop and the average diode current) should be low enough to ensure that the junction temperature is within limits. It is recommended to select fast-recovery diodes with a recovery time less than 50ns, or Schottky diodes with low junction capacitance.

For this application a 100V, 16A, ultra-fast recovery rectifier diode VS-16CTQ100SPBF from Vishay is selected as a secondary rectifier diode.

## **Step 9: Bias Winding Supply Configuration**

The MAX17595 is implemented with a 20V  $V_{\text{IN}}$  UVLO wake-up level with 13V hysteresis to optimize the size of bias capacitor. A simple RC circuit is used to start up the MAX17595. To sustain the operation of the circuit, the input supply to the IC is bootstrapped through diode D2 as shown in Figure 8.

Use  $V_{\text{BIAS}}$  = 12V. Bias winding turns ratio  $k_{\text{b}}$  can be calculated as follows:

$$k_b = k \times \frac{V_{BIAS} + V_{D2}}{V_{OUT} + V_{D1}} = 0.065 \times \frac{12 + 0.8}{5 + 0.1} = 0.165$$

In isolated applications where a bias winding configuration is used to power up the MAX17595,  $C_{\text{START}}$  can be calculated as follows:

$$C_{START} = 0.75 \times (C_{DRV} + 0.1 \times I_{IN} \times t_{SS} + 0.04 \times t_{SS} \times Q_G \times f_{SW})$$

$C_{\mathsf{START}}$  is the startup capacitor,  $C_{\mathsf{DRV}}$  is the cumulative capacitor used at the DRV pin,  $I_{\mathsf{IN}}$  is the MAX17595 quiescent current,  $t_{\mathsf{SS}}$  is the soft-start time,  $V_{\mathsf{OUT}}$  is the output voltage,  $C_{\mathsf{OUT}}$  is the output capacitor used, and  $Q_{\mathsf{G}}$  is the gate charge of the primary n-channel MOSFET.

Select:

$$C_{DRV}$$

= 1 $\mu$ F

$I_{IN}$  = 2 $m$ A

$Q_{G}$  = 23 $n$ C

$t_{SS}$  = 12 $m$ s

$C_{START}$  = 0.75 x (1 $\mu$  + 0.1 x 2 $m$  x 12 $m$  + 0.4 x 12 $m$  x 23 $n$  x 125 $k$ )

$C_{START}$  = 4.512 $\mu$ F

It is recommended to consider the derating of the startup capacitor. A typical value of 4.7 $\mu$ F is selected as  $C_{START}$ ,  $C_{START}$  = 4.7 $\mu$ F.

R<sub>START</sub> can be calculated as follows:

$$R_{START} = \frac{(V_{START} - 10) \times 50}{1 + C_{START}} k\Omega$$

where  $C_{START}$  is in  $\mu F$ .

$$R_{START} = \frac{(218.9 - 10) \times 50}{1 + 4.7} = 1832.4 \text{k}\Omega$$

$R_{START}$  is divided into three equal value resistors of value 308.9k $\Omega$  each. Standard 1206 resistor value of 309k $\Omega$  250mW is selected for  $R_{IN1}$ ,  $R_{IN2}$ , and  $R_{IN3}$ , respectively.

$$R_{IN1} = R_{IN2} = R_{IN3} = 309k\Omega$$

#### Step 10: Feedback Resistor Selection R<sub>U</sub>, R<sub>B</sub>

For all the applications that use a startup network to bias the  $V_{\text{IN}}$  pin during the power-up sequence, calculate the feedback potential divider using the following formulas:

$$R_{B} = \frac{10 \times (30 \times C_{START} - 20 \times C_{DRV} - I_{IN} \times t_{SS})}{V_{OUT} \times C_{OUT} \times (I_{IN} + Q_{G} \times f_{SW})}$$

$$R_{B} = \frac{10 \times (30 \times 4.7 \mu - 20 \times 1 \mu - 2m \times 12m)}{5 \times 180.5 \mu \times (2m + 23n \times 125kHz)} = 184.11\Omega$$

A standard resistor of  $113\Omega$  is selected,  $R_B = 113\Omega$ .

$$R_U = \left(\frac{V_{OUT}}{V_{REF}} - 1\right) \times R_B$$

where  $V_{REF}$  is the reference set by the secondary-side controller ( $V_{REF}$  = 1.24V for TLV431 is used in this design).

$$R_U = \left(\frac{5}{1.24} - 1\right) \times 182 = 0.551 \text{k}\Omega$$

A standard resistor of  $2k\Omega$  is selected,  $R_U = 2k\Omega$ .

#### Step 11: Soft-Start Capacitor

The soft-start period for the devices can be programmed by selecting the value of the capacitor  $C_{SS}$  connected from the SS pin to SGND. Capacitor  $C_{SS}$  can be calculated as:

$$C_{SS} = 8.264 \text{ x t}_{SS}$$

where  $t_{SS}$  is expressed in ms and the resultant value of  $C_{SS}$  is in nF.

$$C_{SS} = 8.264 \text{ x } t_{SS} = 8.264 \text{ x } 12 = 99.17 \text{nF}$$

A standard 100nF is selected as the soft-start capacitor,  $C_{SS}$  = 100nF.

#### **Step 12: Input Capacitor Selection**

The MAX17595 is optimized to implement offline AC-DC applications. In such applications, the input capacitor must be selected based on either the ripple due to the rectified line voltage, or based on holdup-time requirements. Holdup time can be defined as the time period over which the power supply should regulate its output voltage from the instant the AC power fails.

For the flyback converter, the input capacitor supplies the input current when the diode rectifier is off. The voltage discharge on the input capacitor, due to the input average current, should be within the limits specified. Assuming 25% ripple present on input DC capacitor, the input capacitor can be calculated as follows:

$$C_{IN} = \frac{0.045 \times P_{LOAD}}{\eta \times V_{INIPK}^2}$$

where:

$\eta$  = Target efficiency = 85%

$P_{1,OAD} = 24 \times 3 = 72W$

V<sub>INPK</sub> = Peak voltage at minimum AC voltage = 145.6V

$$C_{IN} = \frac{0.045 \times 3.5}{0.87 \times 248.9^2} = 2.922 \mu F$$

#### **Step 13: Output Capacitor Selection**

X7R ceramic output capacitors are preferred in industrial applications due to their stability over temperature. The output capacitor is usually sized to support a step load of a certain percentage of the rated output current so that the output voltage deviation is contained to 3% of the rated output voltage. The output capacitance can be calculated by using the below expressions:

$$t_{\text{RESPONSE}} \cong \left(\frac{0.33}{f_{\text{C}}} + \frac{1}{f_{\text{SW}}}\right)$$

$$C_{\text{OUT}} = \frac{I_{\text{STEP}} \times t_{\text{RESPONSE}}}{\Delta V_{\text{OUT}}}$$

where  $I_{STEP}$  is the load step,  $t_{RESPONSE}$  is the response time of the controller,  $\Delta V_{OUT}$  is the allowable output voltage deviation, and  $f_C$  is the target closed-loop crossover frequency. In our application, we selected  $f_C$  = 12.5kHz, typical bandwidth at nominal voltage for isolated applications to minimize noise and proportionally increase the gain.

$$\begin{split} I_{STEP} &= 0.5 \times I_{OUT} = 0.5 \times 0.7 = 0.35 A \text{ (50\% of } I_{OUT}) \\ &\Delta V_{OUT} = 0.03 \times 5 = 150 \text{mV (3\% of } V_{OUT}, \text{typ)} \\ &t_{RESPONSE} \cong \left(\frac{0.33}{5 k} + \frac{1}{125 k}\right) = 74 \mu \text{s} \\ C_{OUT} &= \frac{I_{STEP} \times t_{RESPONSE}}{\Delta V_{OUT}} = \frac{0.35 \times 74 \mu}{0.150} = 172.66 \mu \text{F} \end{split}$$

Due to the DC-bias characteristics, 8 x 10 $\mu$ F 50V capacitors are selected as  $C_{OUT}$  for this design.

Capacitor values change with temperature and applied voltage. Refer to the capacitor data sheets to select capacitors that guarantee the required output capacitance across the operating range. For design calculations, use the worst-case derated value of capacitance, based on temperature range and applied voltage. In our case the worst-case derated value of capacitors is 48µF.

For the flyback converter, the output capacitor supplies the load current when the main switch is on, and therefore the output voltage ripple is a function of load current and duty cycle. Use the following expression to estimate the output capacitor ripple:

$$\begin{split} \Delta V_{COUT} = & \frac{I_{OUT} \times \left[I_{PRIPEAK} - \left(K \times I_{OUT}\right)\right]^2}{I_{PRIPEAK}^2 \times f_{SW} \times C_{OUT}} \\ \Delta V_{COUT} = & \frac{0.7 \times \left[0.152 - \left(0.065 \times 0.7\right)\right]^2}{0.152^2 \times 125 \text{kHz} \times 180.4 \mu} = 15.15 \text{mV} \end{split}$$

#### **Step 14: Loop Compensation**

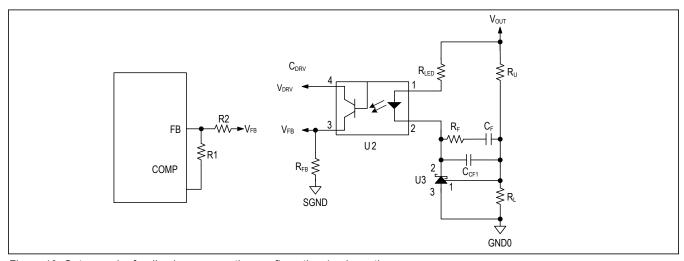

Optocoupler feedback is used in isolated flyback converter designs for precise control of isolated output voltage. Figure 9 shows the overall scheme of the optocoupler feedback.

Use  $R_{FB}$  = 470 $\Omega$  (typ), for an optocoupler transistor current of 1mA. Select R1 = 49.9k $\Omega$  and R2 = 22k $\Omega$  (typical values) to use the full range of available COMP voltage. U3 is a low-voltage adjustable shunt regulator with a 1.24V reference voltage. In this design a 1.24V, 0.5% shunt regulator TLV431BFTA from Diodes Inc. is selected.

Calculate R<sub>LED</sub> using expression below:

$$R_{LED}$$

= 400 x CTR x ( $V_{OUT}$  - 2.7)

$R_{LED}$  = 400 x 1 x (24 - 2.7) = 8.52k $\Omega$

A standard  $8.66k\Omega$  resistor is selected,  $R_{LED} = 8.66k\Omega$ .

The bandwidth of typical optocouplers limits the achievable closed-loop bandwidth of opto-isolated converters. Considering this limitation, the closed-loop crossover frequency can be chosen at the nominal input voltage by selecting  $f_C = 12.5 kHz$ . Closed-loop compensation values are designed based on the open-loop gain at the desired crossover frequency,  $f_C$ . The open-loop at  $f_C$  is calculated using the following expressions.

$$\begin{split} f_{P} = & \frac{I_{OUT}}{\pi \times V_{OUT} \times C_{OUT}} = \frac{0.7}{\pi \times 5 \times 180.4 \mu} = 246.9 \text{Hz} \\ G_{PLANT} = & \frac{f_{P}}{f_{C}} \times \sqrt{\frac{L_{PRI} \times f_{SW} \times V_{OUT}}{8 \times I_{OUT}}} \times \\ & \frac{V_{IN}}{V_{IN} \times R_{CS} + 50 \times 10^{3} \times L_{PRI}} \end{split}$$

$$\begin{split} G_{PLANT} = & \frac{246.9}{5 \text{kHz}} \times \sqrt{\frac{3m \times 125 \text{k} \times 5}{8 \times 0.7}} \times \\ & \frac{325.26}{325.6 \times 1600 m + 50 \times 10^3 \times 3m} \\ G_{PLANT} = & 0.0493 \times 18.29 \times 0.50 = 0.4578 \end{split}$$

Three controller configurations are suggested in **Application Note 5504** based on open-loop gain and the  $R_{LED}$  value. For typical designs, the current transfer ratio (CTR) of the optocoupler designs can be assumed to be unity. It is known that the comparator and gate-driver delays associated with the input voltage variations affect the optocoupler CTR. Depending on the optocoupler selected, variations in CTR causes wide variations in bandwidth of the closed-loop system across the input-voltage operating range. It is recommended to select an optocoupler with

less CTR variations across the operating range. Checking the condition as stated in **Application Note 5504**:

$$\begin{aligned} G_{PLANT} \times CTR \times \frac{R_{FB}}{R_{LED}} \times \frac{R_{1}}{R_{2}} = \\ 0.4578 \times 1 \times \frac{470}{0.931 k} \times \frac{49.9 k}{22 k} = 0.5361 \end{aligned}$$

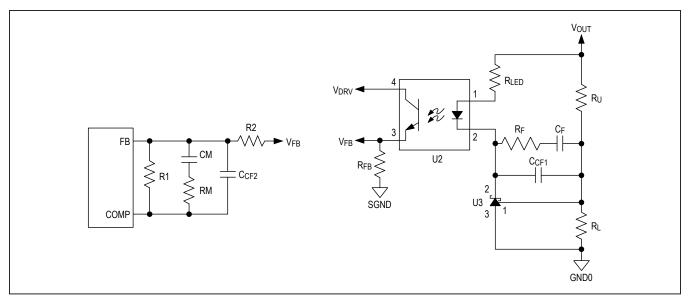

As 0.308 < 0.8, therefore, as stated in **Application Note 5504**, configuration 3 is selected. Figure 10 shows a typical schematic of configuration 3. The  $R_F$  value can be calculated from the expression below:

$$\begin{split} R_F = & \left[ \frac{R_{LED} \times R2}{G_{PLANT} \times CTR \times R_{FB} \times R1} - 1 \right] \times R_U \\ R_F = & \left[ \frac{0.931 k\Omega \times 22 k\Omega}{0.4578 \times 1 \times 470 \times 49.9 k\Omega} - 1 \right] \times 0.549 k\Omega = 0.487 k\Omega \end{split}$$

A typical value of  $4.7k\Omega$  is selected as  $R_F$ ,  $R_F$  =  $4.7k\Omega$ . The  $C_F$  value can be calculated from the expression below:

$$C_{F} = \frac{1}{2\pi \times (R_{U} + R_{F}) \times f_{P}} = \frac{1}{2\pi \times (0.549 \text{k}\Omega + 0.487 \text{k}\Omega) \times 246.8} = 622.5 \text{nF}$$

A standard 27nF capacitor is selected as  $C_F$ ,  $C_F$  = 27nF. The  $C_{CF1}$  value can be calculated from the expression below:

$$C_{CF1} = \frac{1}{\pi \times R_F \times f_{SW}}$$

$$= \frac{1}{\pi \times 0.487 \text{k}\Omega \times 125 \text{kHz}} = 5431 \text{pF}$$

A standard 510pF capacitor is selected as  $C_{CF1}$  = 510pF.

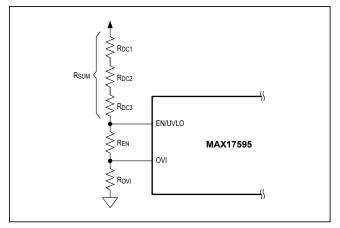

#### Step 15: EN/UVLO and OVI Setting

The device's EN/UVLO pin serves as an enable/disable input, as well as an accurate programmable input UVLO pin. The device does not commence startup operation unless the EN/UVLO pin voltage exceeds 1.21V. The device turns off if the EN/UVLO pin voltage falls below 1.15V. A resistor-divider from the input DC bus to ground can be used to divide down and apply a fraction of the input DC voltage ( $V_{\rm DC}$ ) to the EN/UVLO pin. The values of the resistor-divider can be selected so the EN/UVLO

pin voltage exceeds the 1.23V turn-on threshold at the desired input DC bus voltage. The same resistor-divider can be modified with an additional resistor ( $R_{\text{OVI}}$ ) to implement input overvoltage protection in addition to the EN/UVLO functionality as shown in Figure 11.

When voltage at the OVI pin exceeds 1.21V the devices stop switching and resume switching operations only if voltage at the OVI pin falls below 1.15V. For given values of startup DC input voltage ( $V_{START}$ ) and input overvoltage-protection voltage ( $V_{OVI}$ ), the resistor values for the divider can be calculated as follows:

Select  $R_{OVI} = 24.9k\Omega$ .

$$R_{EN} = R_{OVI} \times \left( \frac{V_{OVI}}{V_{START}} - 1 \right)$$

where  $V_{OVI}$  = maximum allowed overvoltage = 135 x 1.414 = 190.9V.

$$R_{EN} = 24.9k \times \left(\frac{410.12}{218.9} - 1\right) = 21.75k\Omega$$

A standard  $16.2k\Omega$  resistor is selected, where  $R_{EN}$  =  $16.2k\Omega$ .

The same resistor-divider can be modified to implement input overvoltage protection. When the voltage at the OVI pin exceeds 1.215V (typ), the device stops switching. The device resumes switching operations only if the voltage at the OVI pin falls below 1.1V (typ).

$$R_{SUM} = \left[R_{OVI} + R_{EN}\right] \times \left[\frac{V_{START}}{1.21} - 1\right]$$

$$R_{SUM} = \left[24.9k + 22k\right] \times \left[\frac{218.9}{1.21} - 1\right] = 8393k\Omega$$

In universal AC input applications,  $R_{SUM}$  may need to be implemented as equal resistors in series ( $R_{DC1}$ ,  $R_{DC2}$ , and  $R_{DC3}$ ) so that voltage across each resistor is limited to its maximum operation voltage.

$$R_{DC1} = R_{DC2} = R_{DC3} = \frac{8393}{3} k\Omega = 2.79 M\Omega$$

A standard 1.3M  $\!\Omega\!$  resistor is selected for  $R_{DC1},\,R_{DC2},$  and  $R_{DC3}.$

Figure 9. A typical opto-coupler-based feedback compensation.

Figure 10. Opto-coupler feedback compensation configuration 1 schematic.

Figure 11. Programming EN/UVLO and OVI.

# **Design Resources**

Download the complete set of **Design Resources** including the schematics, bill of materials, PCB layout, and test files.

www.maximintegrated.com Maxim Integrated | 10

# **Revision History**

| REVISION<br>NUMBER | REVISION<br>DATE | DESCRIPTION                                                     | PAGES<br>CHANGED |

|--------------------|------------------|-----------------------------------------------------------------|------------------|

| 0                  | 1/18             | Initial release                                                 | _                |

| 1                  | 3/18             | In Table 1, increased the maximum efficiency from 85% to 86.7%. | 1                |

| 2                  | 4/18             | Updated Figure 7.                                               | 3                |

| 3                  | 7/18             | Updated Step 6: MOSFET Selection section.                       | 5                |

Maxim Integrated www.maximintegrated.com

Maxim Integrated cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim Integrated product. No circuit patent licenses are implied. Maxim Integrated reserves the right to change the circuitry and specifications without notice at any time. The parametric values (min and max limits) shown in the Electrical Characteristics table are guaranteed. Other parametric values quoted in this data sheet are provided for guidance.